- 您现在的位置:买卖IC网 > Sheet目录250 > SFCF2048H1BO2TO-I-M0-523-SMA (Swissbit NA Inc)FLASH SLC UDMA/MDMA/PIO 2G

�� �

�

�

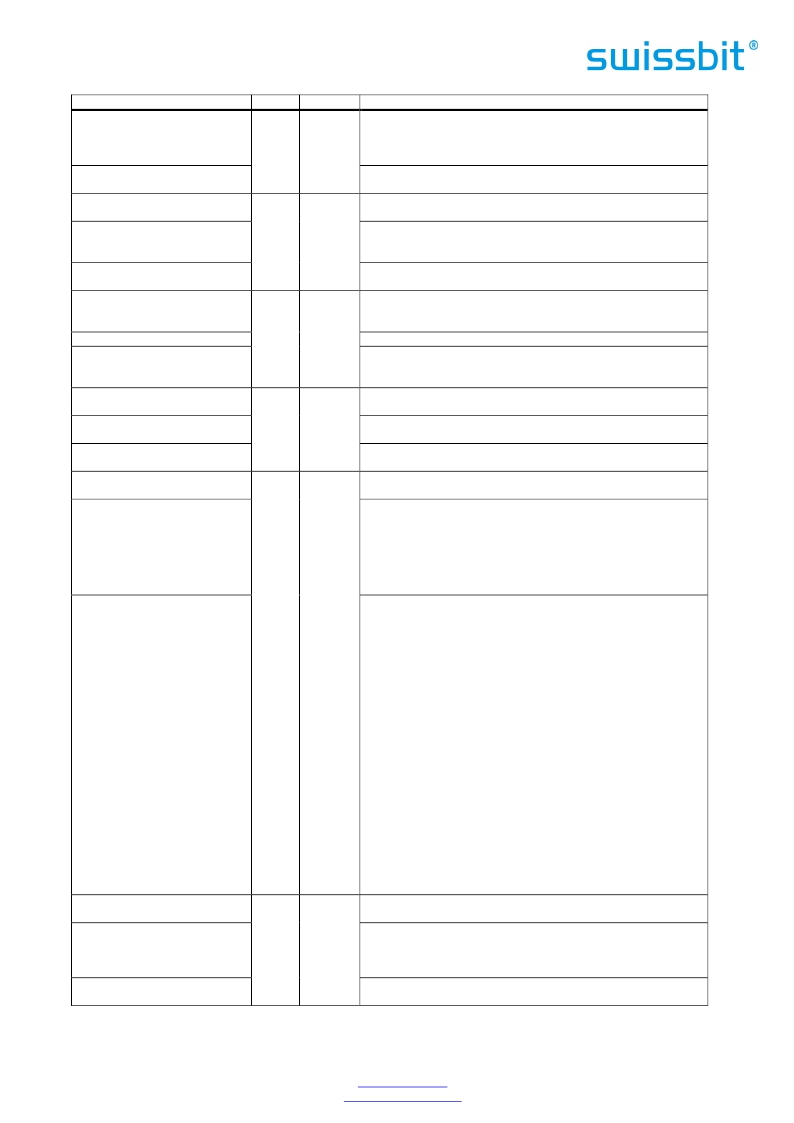

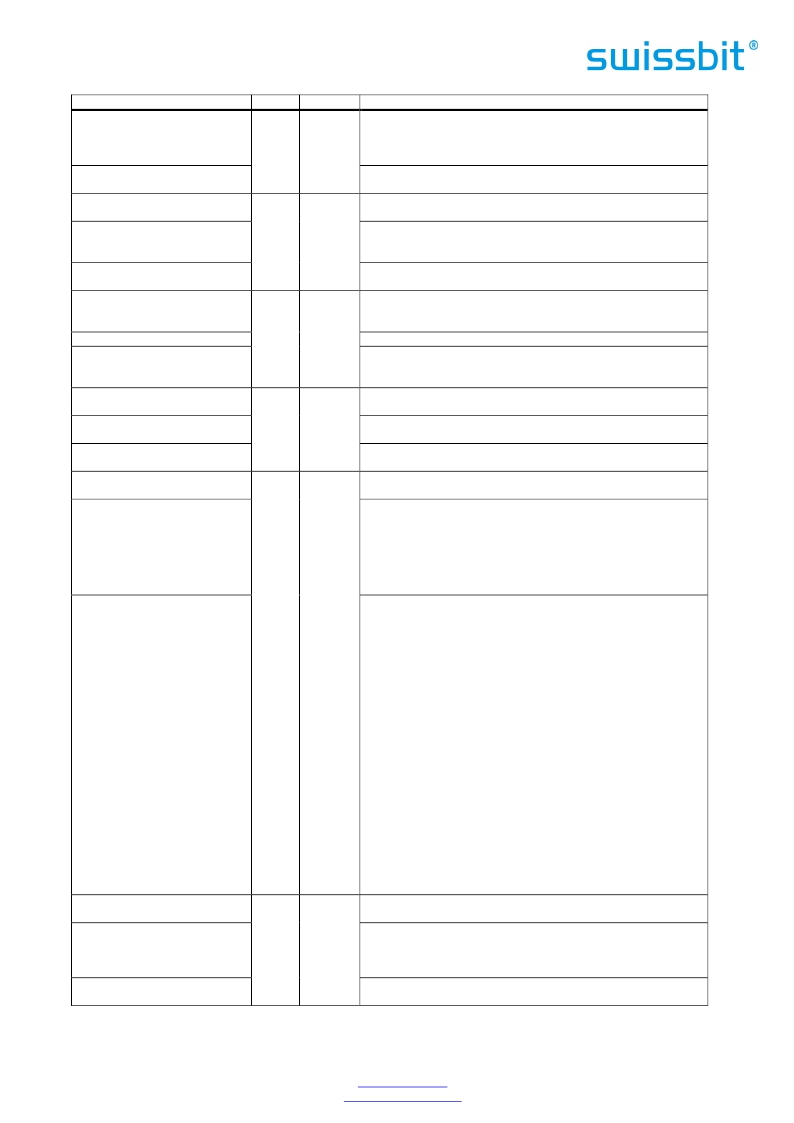

�Signal� Name�

�Dir.�

�Pin�

�Description�

�This� signal� is� asserted� low� to� alert� the� host� to� changes� in� the�

�–� STSCHG�

�(PC� Card� I/O� Mode)�

�–� PDIAG�

�(True� IDE� Mode)�

�BVD2�

�(PC� Card� Memory� Mode)�

�READY� and� Write� Protect� states,� while� the� I/O� interface� is�

�configured.� Its� use� is� controlled� by� the� Card� Config� and� Status�

�Register.�

�In� the� True� IDE� Mode,� this� input� /� output� is� the� Pass� Diagnostic�

�signal� in� the� Master� /� Slave� handshake� protocol.�

�This� signal� is� asserted� high,� as� BVD2� is� not� supported.�

�–� SPKR�

�(PC� Card� I/O� Mode)�

�–� DASP�

�(True� IDE� Mode)�

�I/O�

�45�

�This� line� is� the� Binary� Audio� output� from� the� card.� If� the� Card�

�does� not� support� the� Binary� Audio� function,� this� line� should� be�

�held� negated.�

�In� the� True� IDE� Mode,� this� input/output� is� the� Disk� Active/Slave�

�Present� signal� in� the� Master/Slave� handshake� protocol.�

�These� lines� carry� the� Data,� Commands� and� Status� information�

�D15-D00� (PC� Card� Memory� Mode)�

�31,� 30,� 29,� between� the� host� and� the� controller.� D00� is� the� LSB� of� the� Even�

�28,� 27,� 49,� Byte� of� the� Word.� D08� is� the� LSB� of� the� Odd� Byte� of� the� Word.�

�D15-D00� (PC� Card� I/O� Mode)�

�D15-D00� (True� IDE� Mode)�

�GND�

�(PC� Card� Memory� Mode)�

�I/O�

�48,� 47,� 6,� This� signal� is� the� same� as� the� PC� Card� Memory� Mode� signal.�

�5,� 4,� 3,� 2,� In� True� IDE� Mode,� all� Task� File� operations� occur� in� byte� mode�

�23,� 22,� 21� on� the� low� order� bus� D[7:0]� while� all� data� transfers� are� 16� bit�

�using� D[15:0].�

�Ground.�

�GND�

�(PC� Card� I/O� Mode)�

�GND�

�(True� IDE� Mode)�

�–� INPACK�

�(PC� Card� Memory� Mode)�

�–� INPACK�

�(PC� Card� I/O� Mode)�

�DMARQ�

�(True� IDE� Mode)�

�–� IORD�

�(PC� Card� Memory� Mode)�

�O�

�1,� 50�

�43�

�Same� for� all� modes.�

�Same� for� all� modes.�

�This� signal� is� not� used� in� this� mode.�

�The� Input� Acknowledge� signal� is� asserted� by� the� CompactFlash�

�Storage� Card� when� the� card� is� selected� and�

�responding� to� an� I/O� read� cycle� at� the� address� that� is� on� the�

�address� bus.� This� signal� is� used� by� the� host� to� control� the�

�enable�

�of� any� input� data� buffers� between� the� CompactFlash� Storage�

�Card� and� the� CPU.�

�This� signal� is� a� DMA� Request� that� is� used� for� DMA� data� transfers�

�between� host� and� device.� It� shall� be� asserted� by� the� device�

�when� it� is� ready� to� transfer� data� to� or� from� the� host.� For�

�Multiword� DMA� transfers,� the� direction� of� data� transfer� is�

�controlled� by� –� IORD� and� –� IOWR.� This� signal� is� used� in� a�

�handshake� manner� with� –� DMACK,� i.e.,� the� device� shall� wait�

�until�

�the� host� asserts� –� DMACK� before� negating� DMARQ,� and�

�reasserting�

�DMARQ� if� there� is� more� data� to� transfer.�

�DMARQ� shall� not� be� driven� when� the� device� is� not� selected.�

�While� a� DMA� operation� is� in� progress,� -CS0� and� –� CS1� shall� be�

�held� negated� and� the� width� of� the� transfers� shall� be� 16� bits.�

�If� there� is� no� hardware� support� for� DMA� mode� in� the� host,� this�

�output� signal� is� not� used� and� should� not� be� connected� at� the�

�host.� In� this� case,� the� BIOS� must� report� that� DMA� mode� is� not�

�supported� by� the� host� so� that� device� drivers� will� not� attempt�

�DMA� mode.�

�A� host� that� does� not� support� DMA� mode� and� implements� both�

�PCMCIA� and� True-IDE� modes� of� operation� need� not� alter� the�

�PCMCIA� mode� connections� while� in� True-IDE� mode� as� long� as�

�this� does� not� prevent� proper� operation� in� any� mode.�

�This� signal� is� not� used� in� this� mode.�

�This� is� an� I/O� Read� strobe� generated� by� the� host.� This� signal�

�–� IORD�

�(PC� Card� I/O� Mode)�

�I�

�34�

�gates� I/O� data� onto� the� bus� from� the� CompactFlash� Storage�

�Card� when� the� card� is� configured� to� use� the� I/O�

�interface.�

�–� IORD�

�(True� IDE� Mode)�

�In� True� IDE� Mode,� while� Ultra� DMA� mode� is� not� active,� this�

�signal� has� the� same� function� as� in� PC� Card� I/O� Mode.�

�Swissbit� AG�

�Industriestrasse� 4�

�Swissbit� reserves� the� right� to� change� products� or� specifications� without� notice.�

�Revision:� 1.20�

�CH-9552� Bronschhofen�

�Switzerland�

�www.swissbit.com�

�industrial@swissbit.com�

�C-320_data_sheet_CF-HxBO_Rev120.doc�

�Page� 13� of� 101�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SFCF4096H4BK2SA-I-QT-553-SMA

FLASH SLC UDMA/MDMA/PIO 4G

SFCF64GBH2BU4TO-I-NU-517-STD

FLASH SLC UDMA/MDMA/PIO 64GB

SFN08B4702CBQLF7

RES ARRAY 47K OHM 7 RES 8-DFN

SFP1050-12BG

FRONT END AC/DC 1050W 12V

SFP450-12BG

PWR SUP 450W 12V 36.6A W/STANDBY

SFSD1024N1BN1TO-I-DF-151-STD

FLASH MICRO SD CARD IND S-200 1G

SFSD2048L1BN2TO-I-DF-151-STD

FLASH SECURE DGTL CARD SD 2G

SFSD4096L1BN2TO-I-Q2-141-STD

FLASH SECURE DGTL CARD SDHC 4G

相关代理商/技术参数

SFCF2048H1BO2TO-I-M0-533-ZP1

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H1BO2TO-I-M0-543-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H2BU2TO-C-MS-527-STD

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H2BU2TO-I-MS-517-STD

功能描述:FLASH SLC UDMA/MDMA/PIO 2GB RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-440 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF2048H2BU2TO-I-MS-527-STD

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H4BK1SA-C-QT-553-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H4BK1SA-I-QT-553-SMA

功能描述:FLASH SLC UDMA/MDMA/PIO 2G RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-300 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF2048H4BK2SA-C-DS-553-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH SLC UDMA/MDMA/PIO 2G